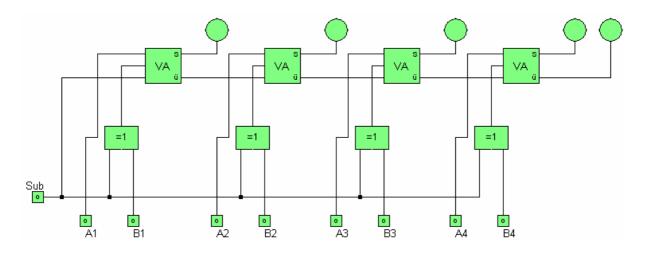

# 4-Bit Addierwerk (Ripple-Carry-Adder)

## Weitere wichtige Schaltfunktionen

NAND (= NOT AND)

Funktionstabelle:

| Α | В | $A \cdot B$ | $\overline{A \cdot B}$ |

|---|---|-------------|------------------------|

| 0 | 0 | 0           | 1                      |

| 0 | 1 | 0           | 1                      |

| 1 | 0 | 0           | 1                      |

| 1 | 1 | 1           | 0                      |

Symbol:

Das NAND ist das negierte AND (UND).

NOR (=NOT OR)

Funktionstabelle:

| А | В | A+B | $\overline{A+B}$ |

|---|---|-----|------------------|

| 0 | 0 | 0   | 1                |

| 0 | 1 | 1   | 0                |

| 1 | 0 | 1   | 0                |

| 1 | 1 | 1   | 0                |

Symbol:

Das NOR ist das negierte OR (ODER).

## Vollständige Systeme

Mit AND, OR und NOR kann man jede beliebige Schaltfunktion realisieren

⇒ Vollständiges System

Mit NAND kann man ebenfalls jede beliebige Schaltfunktion realisieren

⇒ Vollständiges System

NOR ist ebenfalls ein vollständiges System

## Beweis für NAND:

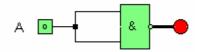

#### NICHT nur mit NAND

$$\overline{A} = \overline{A \cdot A}$$

(Idempotenzgesetz)

Logikplan:

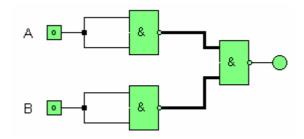

#### ODER nur mit NAND

$$A + B = \overline{(\overline{A + B})} \quad \text{(doppeltes Komplement)}$$

$$= \overline{\overline{A + B}} \quad \text{(De Morgan)}$$

$$= \overline{\overline{A \cdot A \cdot B \cdot B}}$$

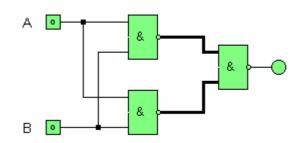

## Logikplan:

#### **UND nur mit NAND**

$$A \cdot B = (A \cdot B) + (A \cdot B) \qquad \text{(Idempotenzgesetz)}$$

$$= \overline{(A \cdot B) + (A \cdot B)} \qquad \text{(doppeltes Komplement)}$$

$$= \overline{\overline{A \cdot B} \cdot \overline{A \cdot B}} \qquad \text{(De Morgan)}$$

## Logikplan:

Funktion in DNF umwandeln in Funktion nur mit NAND

$$y = \left(A \cdot \left(B \cdot \overline{C}\right)\right) + \left(A \cdot C\right)$$

$$= \overline{\left(A \cdot \left(B \cdot \overline{C}\right)\right) + \left(A \cdot C\right)}$$

$$= \overline{A \cdot \left(B \cdot \overline{C}\right)} \cdot \left(\overline{A \cdot C}\right)$$

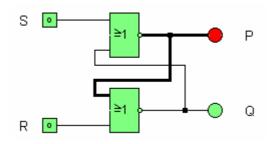

## **RS-Flipflop**

- aufgebaut aus zwei kreuzgekoppelten NOR (oder NAND) Gattern

- Setz und Rücksetzeingang

#### Logikplan:

Fallunterscheidung:

$$S = 1; R = 0 \rightarrow P = 0; Q = 1$$

$$S = 0$$

;  $R = 1 \rightarrow P = 1$ ;  $Q = 0$

$$S = 0$$

;  $R = 0$ ;  $Q = 1 \rightarrow P = 0$ ;  $Q = 1$

$$S = 0$$

:  $R = 0$ :  $Q = 0 \rightarrow P = 1$ :  $Q = 0$

Q ist der gespeicherte Binärwert. Am Anschluss P kann der Wert von Q invertiert abgegriffen werden. Man bezeichnet den Anschluss deshalb auch mit  $\overline{Q}$ .

S = 1; R=1

$$\rightarrow$$

P = O; Q = 0, d.h. P =  $\overline{Q}$  ist verletzt.

→ Diese Situation ist **verboten**, weil sie so nicht definiert ist!

#### Funktionstabelle RS-FF

| Eingangs | Eingangsvariable Zustandsvaria |   | svariable | Ausgangsvariable |                |

|----------|--------------------------------|---|-----------|------------------|----------------|

| S        | R                              | Q | Р         | O <sup>+</sup>   | P <sup>+</sup> |

| 0        | 0                              | 0 | 1         | 0                | 1              |

| 0        | 0                              | 1 | 0         | 1                | 0              |

| 1        | 0                              | 0 | 1         | 1                | 0              |

| 1        | 0                              | 1 | 0         | 1                | 0              |

| 0        | 1                              | 0 | 1         | 0                | 1              |

| 0        | 1                              | 1 | 0         | 0                | 1              |

| 1        | 1                              | 0 | 1         | X                | X              |

| 1        | 1                              | 1 | 0         | Х                | Х              |

Q, P = aktueller Zustand  $Q^+$ ,  $P^+$  = neuer Zustand

Die ersten beiden Zeilen zeigen die Speicherfunktion: Liegt kein Wert an, so wird der aktuelle Wert beibehalten

Die dritte und vierte Zeile zeigen die Setzfunktion: Liegt bei Q eine 1 an, wird sie in den Speicher geschrieben.

Die fünfte und sechste Zeile zeigen die Rücksetzfunktion: Liegt bei R eine 1 an, wird Q auf 0 gesetzt.

Die letzten beiden Zeilen zeigen die unzulässige Einstellung, wenn an beiden Eingängen eine 1 anliegt. Für diese Einstellung werden auf Grund der Nicht-Zulässigkeit in der Funktionstabelle "don't cares" gesetzt.

Weil bei bestimmungsgemäßen Betrieb immer P = Q gilt, wird nachfolgend nur noch Q aufgeführt.

Q ist der gespeicherte Zustand.

Funktionstabelle des RS - FF (nur noch mit Q als Zustand)

| S | R | Q | $Q^{\dagger}$ |

|---|---|---|---------------|

| 0 | 0 | 0 | 0             |

| 1 | 0 | 0 | 1             |

| 0 | 1 | 0 | 0             |

| 0 | 0 | 1 | 0             |

| 1 | 1 | 0 | Χ             |

| 1 | 0 | 1 | 1             |

| 0 | 1 | 1 | 1             |

| 1 | 1 | 1 | Χ             |

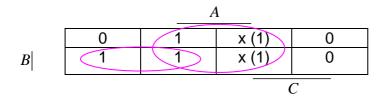

## KV – Diagramm:

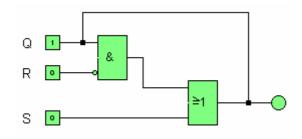

$$Q^+ = S + (Q \cdot \overline{R})$$

(charakteristische Gleichung des RS – FF)

## Logikplan:

## Zeichenerklärung:

Die erstellten Logikpläne haben einige neue Schaltzeichen, die hier kurz erklärt werden.

1) Schalter: Gibt entweder eine 0 oder 1 auf die angeschlossene Leitung aus.

2) LED: Zeigt auch AUS oder AN den Zustand der Ausgangsvariablen an.